基于 Zynq 的振动台控制器架构设计与算法实现-总体架构设计(二)

创始人

2025-05-31 09:16:24

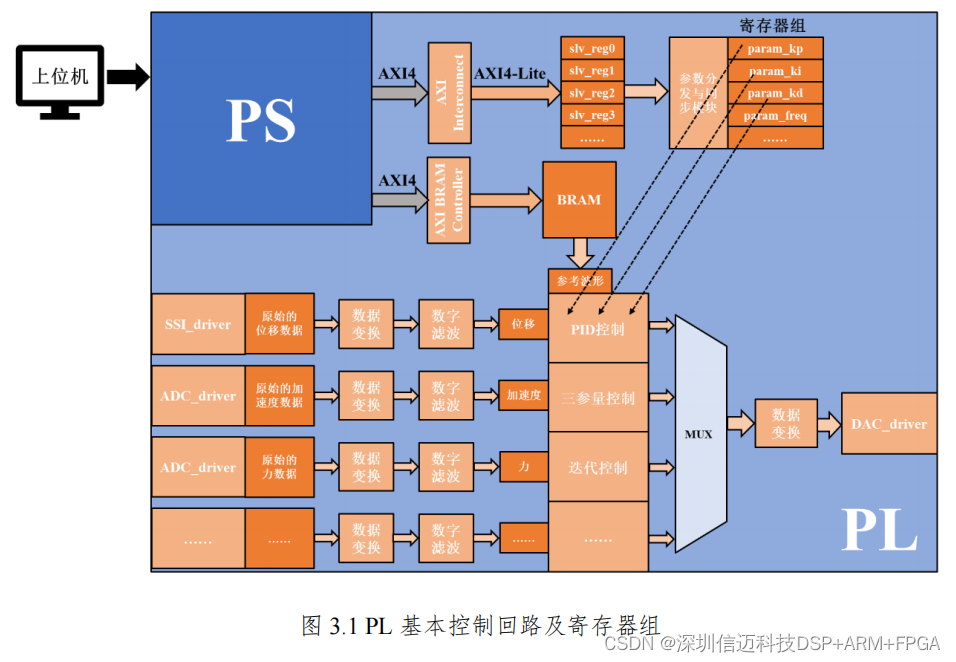

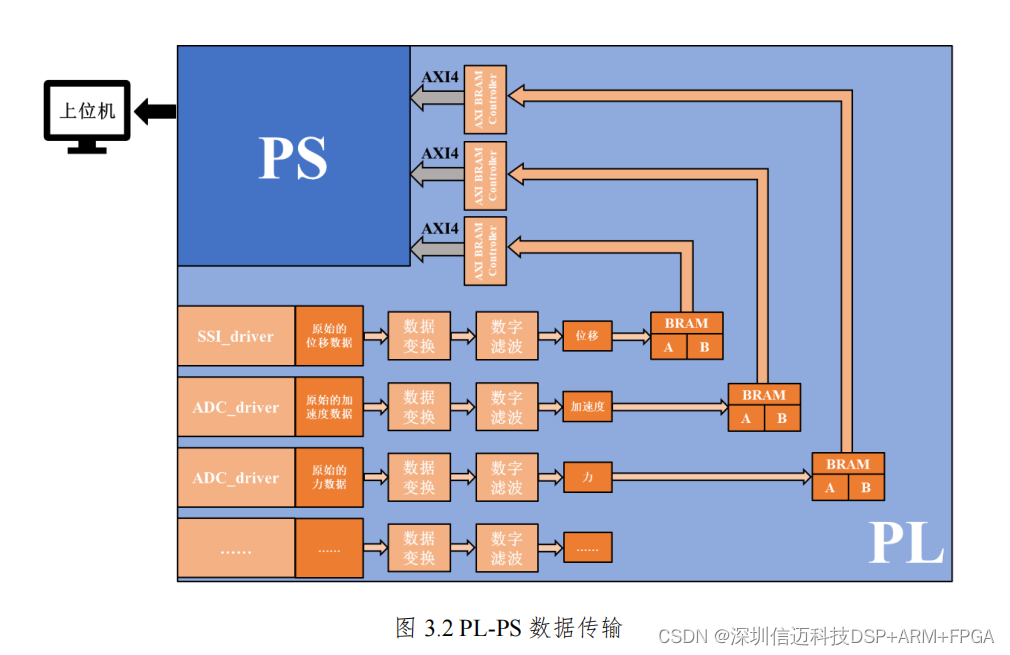

3 振动台控制器架构设计与实现

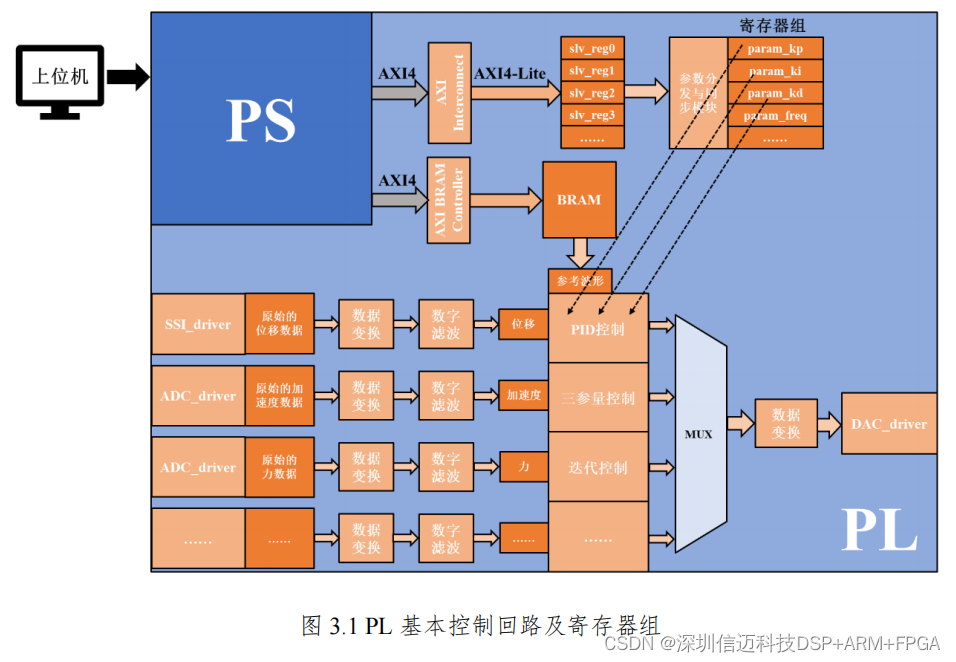

如前所述,Zynq-7000 本身已经具有了独特的架构优势,得益于 Zynq 的

ARM+FPGA 架构,可以将控制器的核心功能分为软硬件两部分去开发,软硬件

协同完成对振动台的控制。对实时性和计算性能要求较高的采样、计算、控制等

部分交给硬件逻辑(PL)完成,而对实时性要求不高的通信等部分交给软件(PS)

完成(注意“实时”和“高速”的区别,通信可能需要高速,但不一定有采样和

控制那么高的实时性要求)。以此为基础,本章设计了 Zynq 振动台控制器的程序

架构。

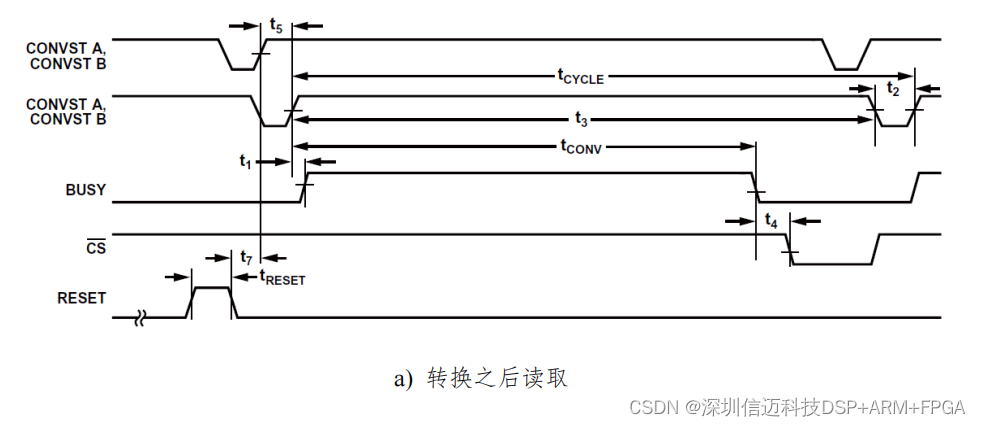

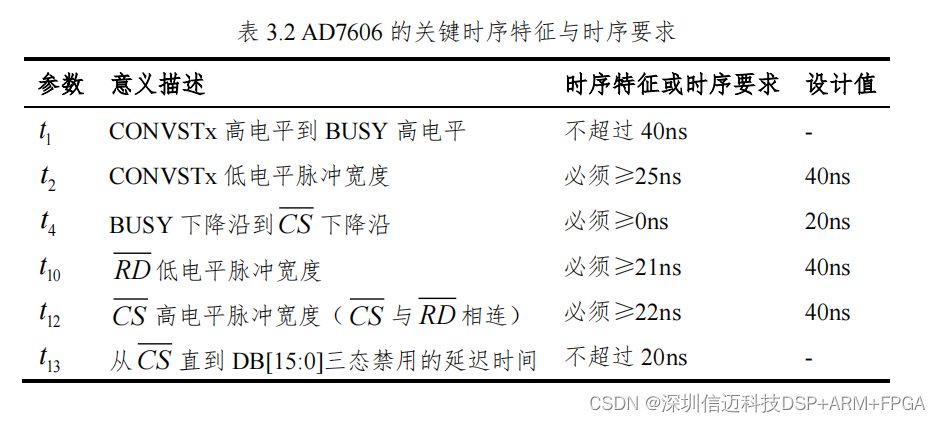

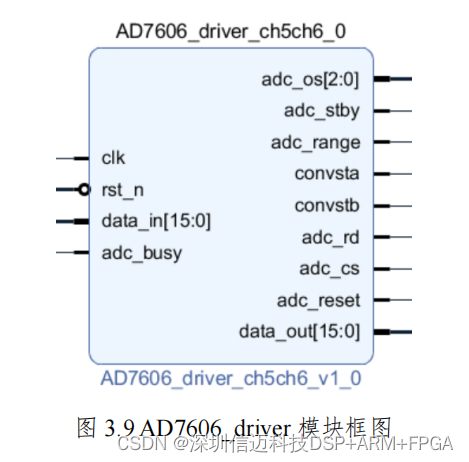

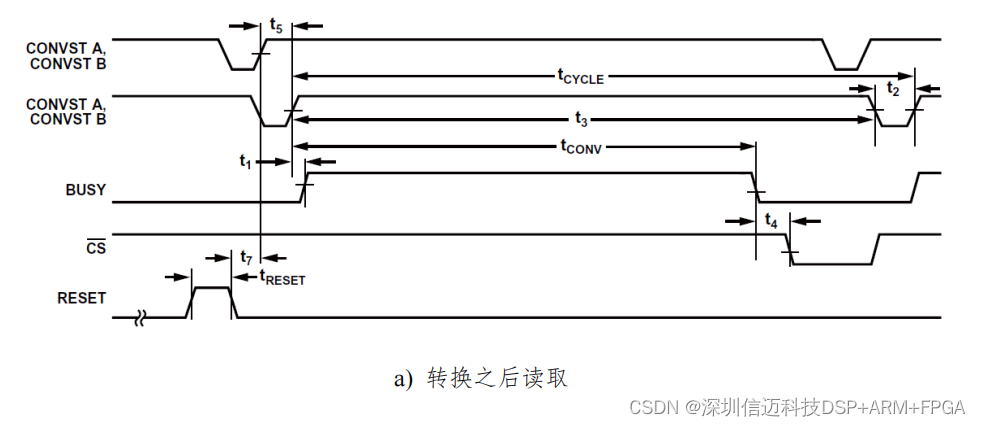

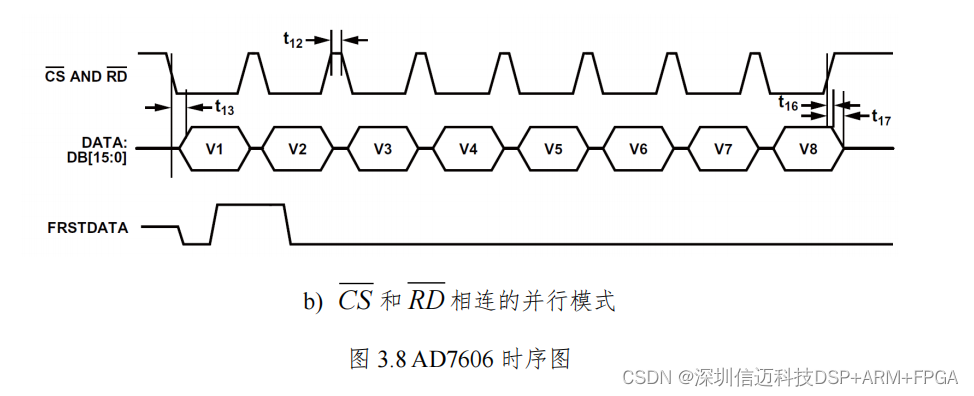

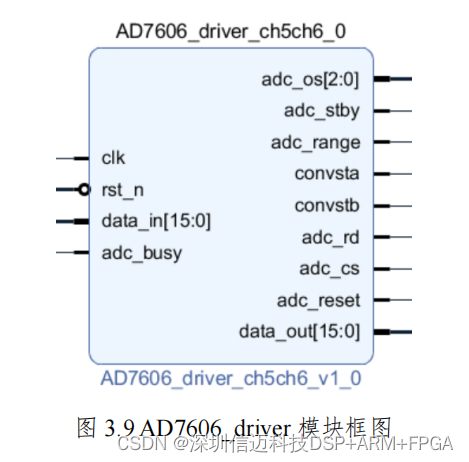

为实现对 ADC 数据的读取,在 FPGA 中设计了 AD7606 的驱动模块

AD7606_driver。模块框图如下图所示。

为实现对 ADC 数据的读取,在 FPGA 中设计了 AD7606 的驱动模块

AD7606_driver。模块框图如下图所示。

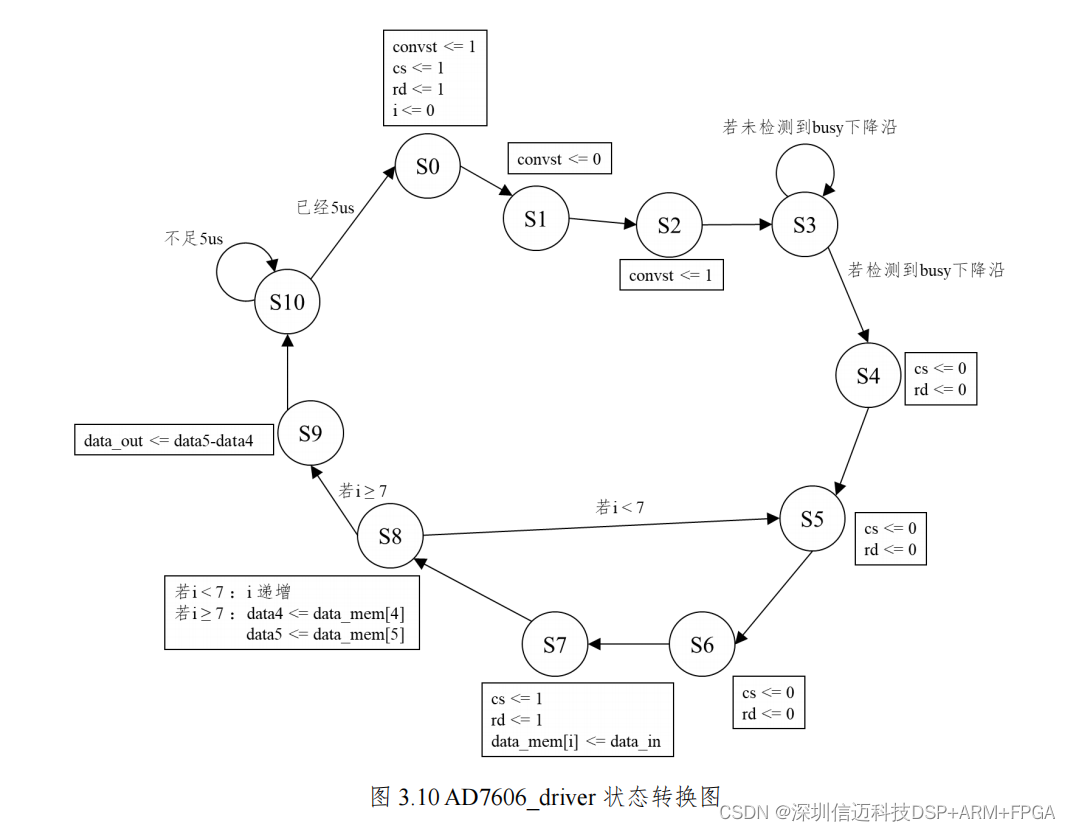

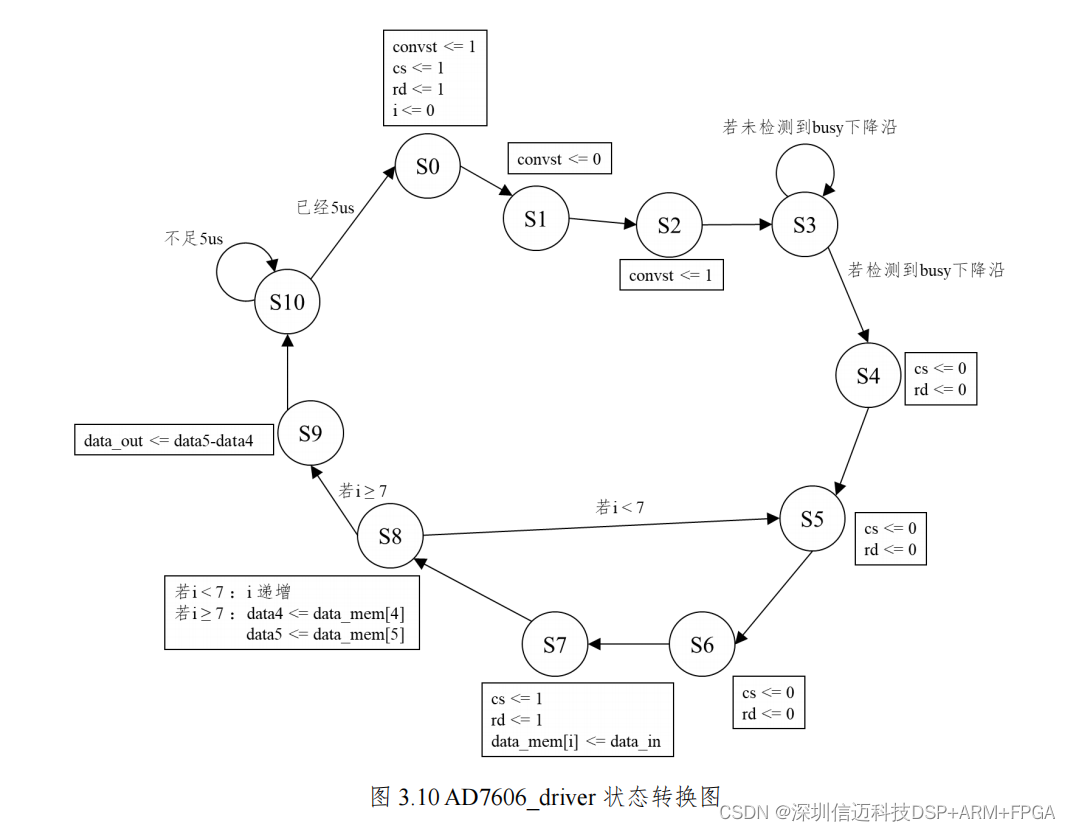

状态转换图如图 3.10 所示。选用最高的采样率 200k,所以一个循环为 5us。

其中检测 busy 下降沿需要打拍操作。

状态转换图如图 3.10 所示。选用最高的采样率 200k,所以一个循环为 5us。

其中检测 busy 下降沿需要打拍操作。

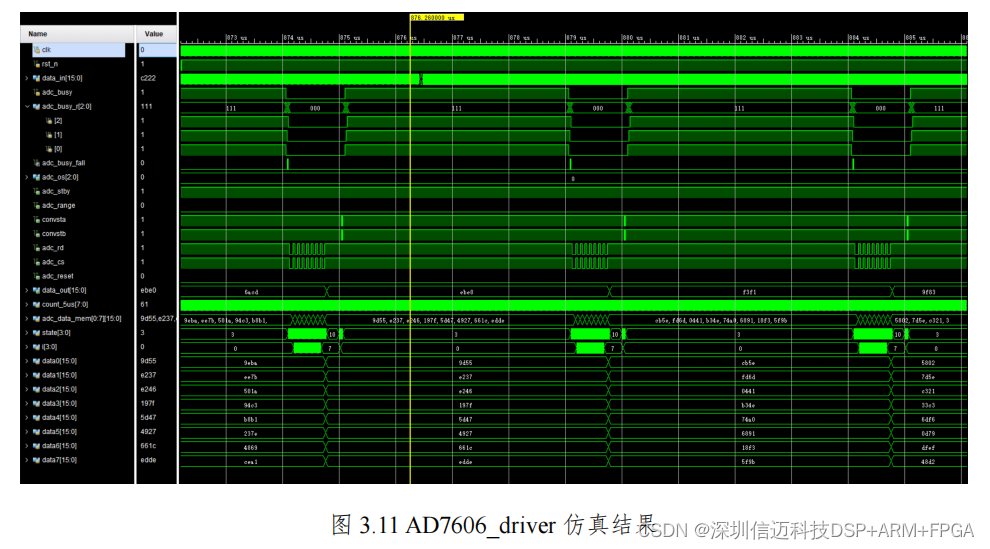

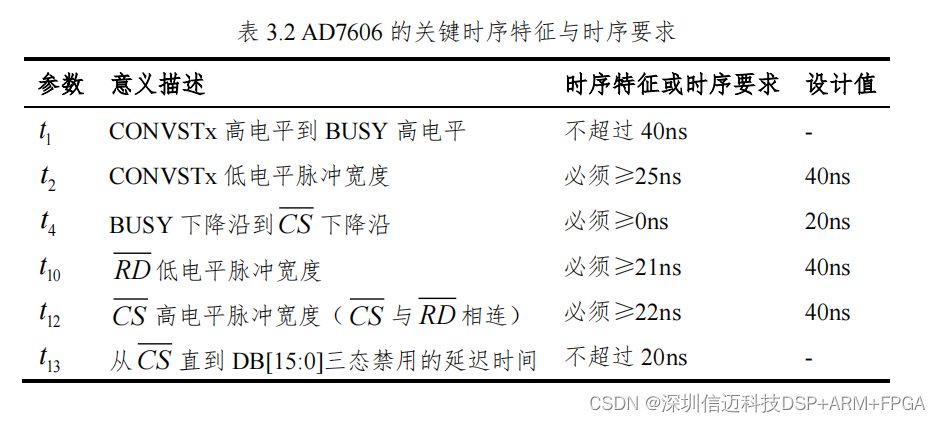

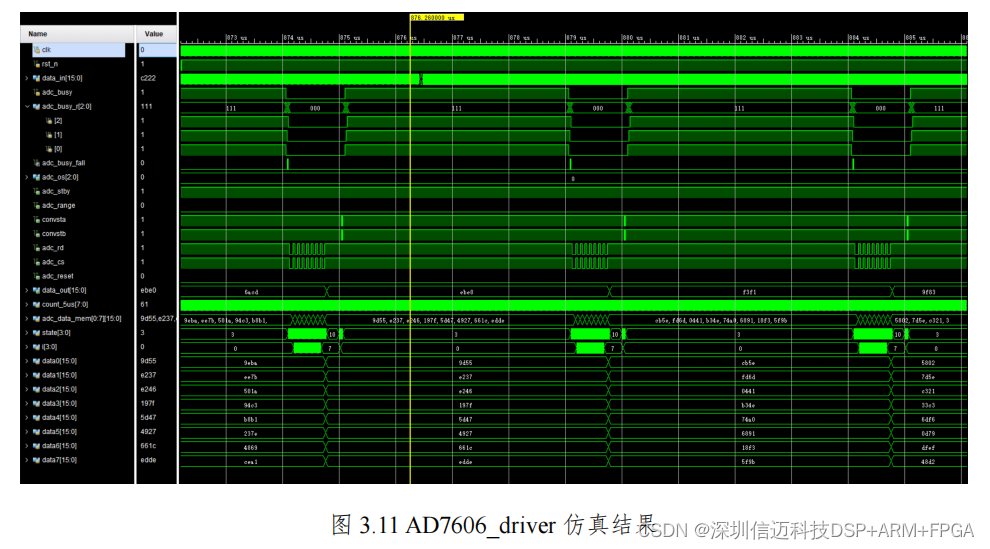

AD7606_driver 模块的仿真结果如下图所示,经过反复修改调试,使其关键

信号符合数据手册中的时序要求。

AD7606_driver 模块的仿真结果如下图所示,经过反复修改调试,使其关键

信号符合数据手册中的时序要求。

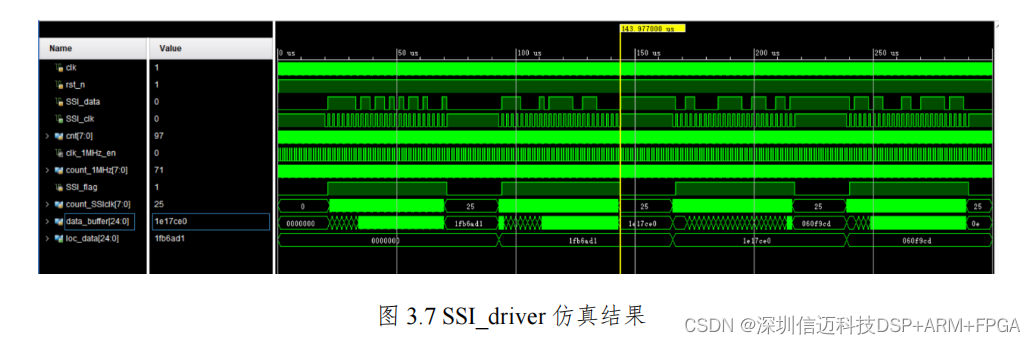

为实现对 SSI 数据的读取,在 FPGA 中设计了 SSI 的驱动模块 SSI_driver。 模块框图如图 3.6 所示。所用的磁致伸缩 SSI 位移传感器是 25 位二进制(Binary) 编码输出的。由于硬件电路中已经支持了差分信号与单端信号的转换,所以这里 只需要单端的 SSI_clk 信号和 SSI_data 信号即可[28]。

SSI_driver 模块的仿真结果如图 3.7 所示。

为实现对 ADC 数据的读取,在 FPGA 中设计了 AD7606 的驱动模块

AD7606_driver。模块框图如下图所示。

为实现对 ADC 数据的读取,在 FPGA 中设计了 AD7606 的驱动模块

AD7606_driver。模块框图如下图所示。

状态转换图如图 3.10 所示。选用最高的采样率 200k,所以一个循环为 5us。

其中检测 busy 下降沿需要打拍操作。

状态转换图如图 3.10 所示。选用最高的采样率 200k,所以一个循环为 5us。

其中检测 busy 下降沿需要打拍操作。

AD7606_driver 模块的仿真结果如下图所示,经过反复修改调试,使其关键

信号符合数据手册中的时序要求。

AD7606_driver 模块的仿真结果如下图所示,经过反复修改调试,使其关键

信号符合数据手册中的时序要求。

信迈提供ZYNQ+AD7606解决方案。

相关内容

热门资讯

STM32开发基础知识入门

C语言基础 位操作 对基本类型变量可以在位级别进行操作。 1) 不改变其他位的值的状况下ÿ...

国内充电基础设施发展缓慢的真正...

今天给各位分享国内充电基础设施发展缓慢的真正原因是什么?cbyl的怂货的知识,其中也会对充电基础设施...

回首掏走位走位什么梗,“回首掏...

回首掏走位走位什么梗目录回手掏什么意思“回首掏”是什么意思?回手掏是什么梗 回手掏什么意思“回手掏,...

带龙凤的成语有啥,龙凤的成语有...

带龙凤的成语有啥目录带龙凤的成语有啥龙凤的成语有哪些有关龙凤的成语和龙凤有关的成语带龙凤的成语有啥 ...

C++演讲比赛流程管理系统_黑...

任务 学校演讲比赛,12人,两轮,第一轮淘汰赛...

复联4有彩蛋吗,《复联4》古一...

复联4有彩蛋吗目录复联4有彩蛋吗《复联4》古一怎么知道五年后的事,为何会把时间宝石交给班纳?《复联4...

labview数据类型转换字符...

wx供重浩:创享日记 对话框发送:labview转换 获取完整无水印报告...

【分享】国内如何使用chatG...

上周,OpenAI宣布正式发布多模态预训练大模型GPT-4,其强大的能力...

软件智能:aaas系统中AI的...

概要(内容概述) <同一>将设计目标确定为“软件智能”的aaas中,AI的任务和AI能...

早日康复祝福语简短8字,早日康...

早日康复祝福语简短8字目录早日康复祝福语简短8字早日康复祝福语简短8字搞定手术祝福语8个字早日康复祝...

淘宝店铺名怎么改,淘宝店铺怎么...

淘宝店铺名怎么改目录淘宝店铺名怎么改淘宝店铺怎么改名淘宝店铺名可以修改吗,怎样修改怎么修改淘宝店铺名...

微信助手怎么查单删 极速百科网...

微信助手怎么查单删目录微信助手怎么查单删微信助手怎么查单删微信如何查单删 2016微信如何知道对方有...

陆家嘴都有什么旅游景点 极速百...

陆家嘴都有什么旅游景点目录陆家嘴都有什么旅游景点陆家嘴都有什么旅游景点陆家嘴有哪些旅游景点上海陆家嘴...

1229 - 拦截导弹的系统数...

1229 - 拦截导弹的系统数量求解 题目描述 某国为了防御敌国的导弹袭击,发展出一种...

如何做好项目缺陷管理

缺陷管理是项目管理工作中的重要环节。Excel表格是国内团队常用的缺陷管理工具,具备上...

Python生成器

1.生成器 生成器是一种特殊的迭代器,它是通过函数来实现的。生成器函数每次执行到yi...

Nginx可视化管理工具 - ...

一、介绍 nginx-proxy-manager 是一个反向代理管理系统,它基于Nginx,具有漂亮...

如何解除迅雷安全模式,迅雷怎样...

如何解除迅雷安全模式目录如何解除迅雷安全模式迅雷怎样解除安全模式迅雷VIP尊享版怎么解除安全模式?迅...

感谢朋友圈留言句子,适合发朋友...

感谢朋友圈留言句子目录感谢朋友圈留言句子适合发朋友圈表达感谢的句子20句发朋友圈的感谢短语有哪些?有...

关于韩娱的小说有没有什么好看的...

关于韩娱的小说有没有什么好看的目录关于韩娱的小说有没有什么好看的求好看的韩娱小说有没有好看的韩娱小说...

什么是表面粗糙度(什么是表面粗...

本篇文章极速百科给大家谈谈什么是表面粗糙度,以及什么是表面粗糙度?它对零件的使用性能有什么影响?对应...

永远用英语怎么说,“永远”除了...

永远用英语怎么说目录永远用英语怎么说“永远”除了“forever”的英文翻译~~还有哪些

少年音怎么练,怎么配出清爽的少...

少年音怎么练目录少年音怎么练怎么配出清爽的少年音?怎么学正太音少年音,像是龙马啊、镜音连啊不二啊那种...

情侣之间的爱称有哪些,情侣称呼...

情侣之间的爱称有哪些目录情侣之间的爱称有哪些情侣称呼有创意的爱称情侣之间好听的称呼都有什么?情侣爱称...

共享汽车怎么租车 极速百科网 ...

共享汽车怎么租车目录共享汽车怎么租车共享汽车怎么租车gofun出行有人开吗?使用方法是什么?共享汽车...

Python应用之爬虫基础:r...

引言 在生活中,大家都使用过浏览器,通过输入要搜索的内容以及鼠标点击等操...

jsp医疗辅助诊断管理系统se...

一、源码特点 JSP医疗辅助诊断管理系统是一套完善的java web信息管理系统ÿ...

db19密钥库和加密

创建密钥库ENCRYPTION_WALLET_LOCATION =(SOURCE =...

开局之年是什么意思(开局之年之...

本篇文章极速百科给大家谈谈开局之年是什么意思,以及开局之年之后是什么年对应的知识点,希望对各位有所帮...

抖音gga什么意思(抖音gg是...

本篇文章极速百科给大家谈谈抖音gga什么意思,以及抖音gg是什么意思对应的知识点,希望对各位有所帮助...